Timer A¶

Timer_A Introduction¶

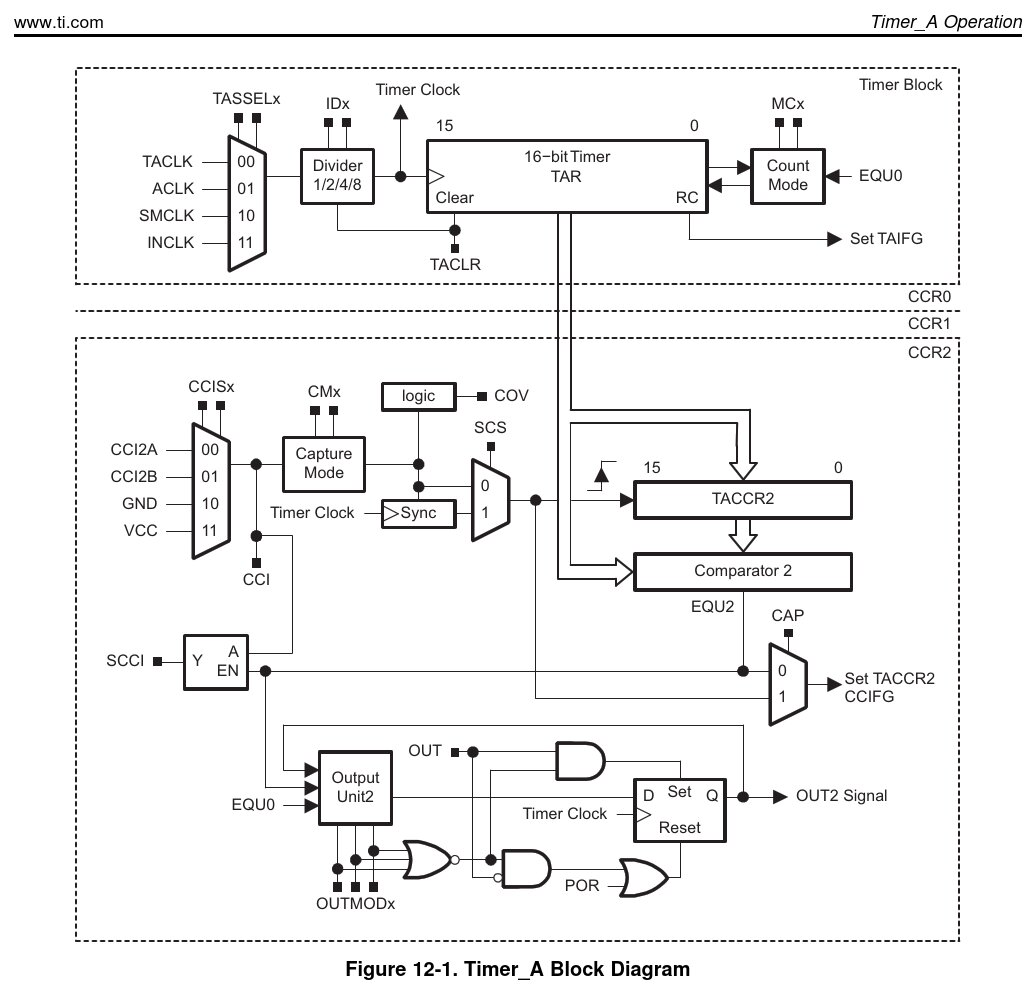

Timer_A is a 16-bit timer/counter with three capture/compare registers. Timer_A can support multiple capture/compares, PWM outputs, and interval timing. Timer_A also has extensive interrupt capabilities. Interrupts may be generated from the counter on overflow conditions and from each of the capture/compare registers.

Timer_A features¶

Asynchronous 16-bit timer/counter with four operating modes

Selectable and configurable clock source

Two or three configurable capture/compare registers

Configurable outputs with PWM capability

Asynchronous input and output latching

Interrupt vector register for fast decoding of all Timer_A interrupts

Registers¶

Registers |

Short Form |

Register Type |

Address |

Initial State |

|---|---|---|---|---|

Timer_A control |

TACTL |

Read/write |

0160h |

Reset with POR |

Timer_A counter |

TAR |

Read/write |

0170h |

Reset with POR |

Timer_A capture/compare control 0 |

TACCTL0 |

Read/write |

0162h |

Reset with POR |

Timer_A capture/compare 0 |

TACCR0 |

Read/write |

0172h |

Reset with POR |

Timer_A capture/compare control 1 |

TACCTL1 |

Read/write |

0164h |

Reset with POR |

Timer_A capture/compare 1 |

TACCR1 |

Read/write |

0174h |

Reset with POR |

Timer_A interrupt vector |

TAIV |

Read only |

012Eh |

Reset with POR |